Project: **Visual Cache Simulator**

Input: Real Addresses

Outputs:

1. Number of Hits

2. Number of Misses

3. Hit Ratio

4. Visual Representation of Cache including

- 4.1. Index or Index Set

- 4.2. Tag

- 4.3. Data

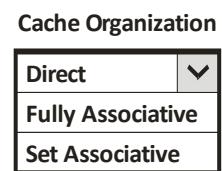

Cache Organizations to be Simulated:

1. Direct-Mapped Cache

2. Fully Associative Cache

3. Set Associative Cache

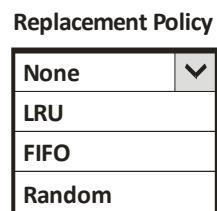

Replacement Policies:

1. Least Recently Used (LRU)

2. First-In First-Out

3. Random

## Prototype Display

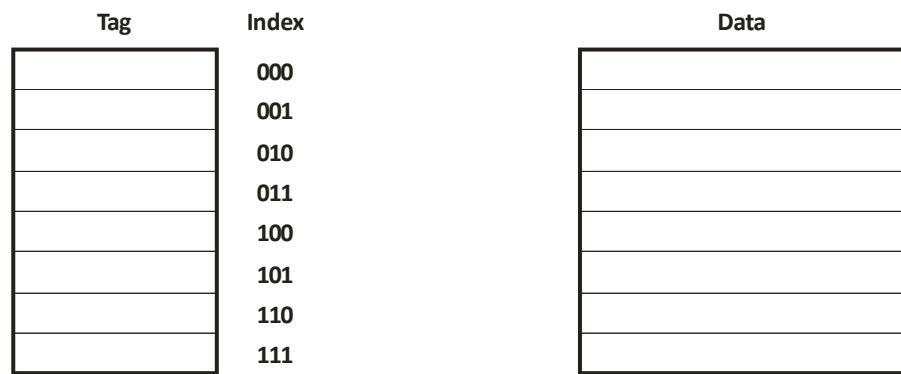

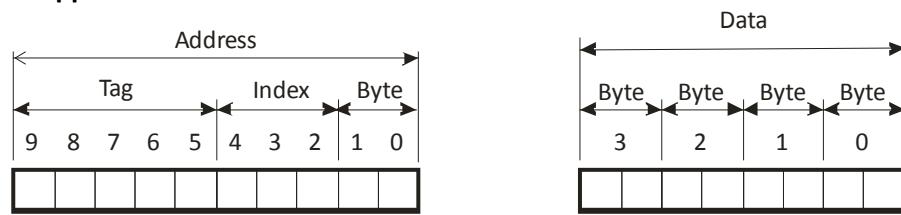

### 1. Direct-Mapped Cache

Next Address

Figure 1. Direct-Mapped Cache Display

Direct-Mapped Cache Operation:

- 1.1 **Cache Organization** drop-down list. The Cache Organization drop-down list is used to select a Direct-Mapped Cache Simulation.

- 1.2 **Replacement Policy** drop-down list. The Replacement Policy drop-down list does not function and None is displayed as the option selected since a Direct-Mapped Cache has only a single option for replacement. The new data and address for a particular index replace the tag and data stored in the cache if the new tag is different from the tag stored in the cache.

- 1.3 **Next Address** button. The Next Address button is used to solicit a new address and data. The new address and data are displayed in the Address and Data boxes. The address is divided into three parts, tag, index, and byte as shown. The address is displayed in binary. Data are represented in hexadecimal.

- 1.4 **Cache** display. The cache is displayed as three columns where each column has as many rows as there are index values. Since the index shown in this example has three (3) bits, there are eight (8) rows. The columns are labeled **Tag**, **Index**, and **Data** respectively. Each time a new address is generated the index row where the tag and data are stored is highlighted. Two levels of highlighting are used. A bright highlight is employed if the tag and data are replacing an existing tag and data. A lesser highlight is employed if the tag and data are found in the cache. Initially all tags and data are blank. Tags are displayed in binary. Data are displayed in hexadecimal. Index values are fixed as labels for each row.

- 1.5 **Hit** box. The hit box records the number of times that address is found in the cache.

- 1.6 **Miss** box. The miss box records the number of times the address cannot be found in the cache.

- 1.7 **Hit Ratio** box. The ratio box records the fraction found by dividing the number of hits by the total number of addresses.

- 1.8 **Address** box. The address box displays the three components of the address, tag, index, and byte for each new address generated.

- 1.9 **Data** box. The data box displays the contents of the address given in the Address box. Eight hexadecimal digits are displayed.

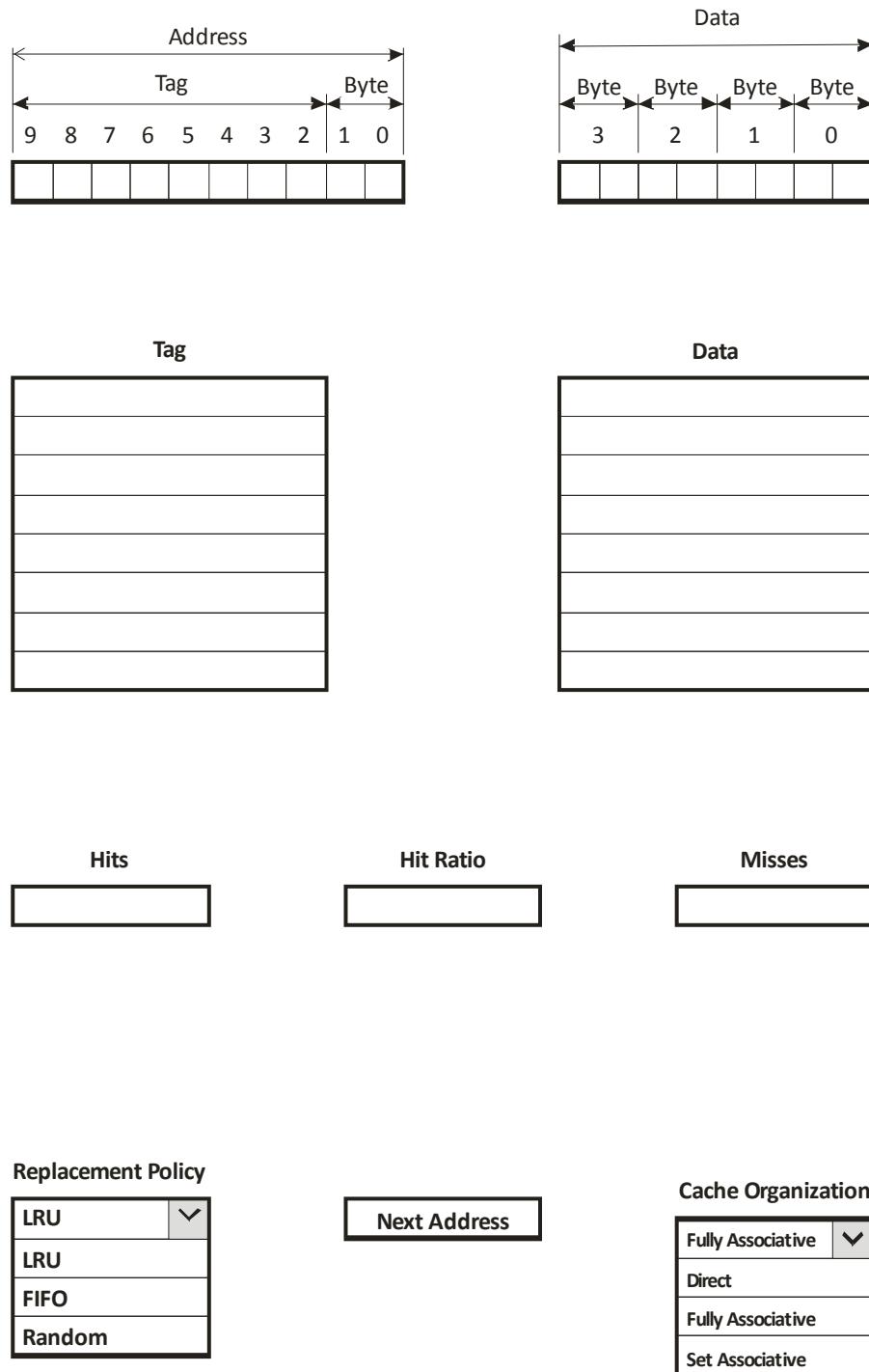

## 2 Fully Associative Cache

**Figure 2.** Fully Associative Cache Display

**2.1 Cache Organization** drop-down list. The Cache Organization drop-down list is used to select a **Fully Associative Cache Simulation**.

**2.2 Replacement Policy** drop-down list. The Replacement Policy drop-down list permits one of three selections: **LRU**, **FIFO**, or **Random**. When LRU is selected the cache replaces the least recently used tag and data in the event of a cache miss. When FIFO is selected the cache replaces the oldest tag

and data in the cache in the event of a cache miss. When Random is selected the cache random selects a tag and data to replace on a cache miss.

**2.3 Next Address** button. The Next Address button is used to solicit a new address and data. The new address and data are displayed in the Address and Data boxes. The address is divided into three parts, tag, index, and byte as shown. The address is displayed in binary. Data are represented in hexadecimal.

**2.4 Cache** display. The cache is displayed as two columns where each column has as many rows as there are index values in the direct-mapped cache. Since the index in the direct-mapped cache has three (3) bits, there are eight (8) rows. The columns are labeled **Tag** and **Data** respectively. Each time a new address is generated the row where the tag and data are stored is highlighted. Three levels of highlighting are used. A bright highlight is employed if the tag and data are replacing an existing tag and data. A middle highlight is employed if the tag and data are found in the cache. A lesser highlight is used to identify the next tag and data to be replaced in the event of a cache miss. Initially all tags and data are blank. Tags are displayed in binary. Data are displayed in hexadecimal.

**2.5 Hit** box. The hit box records the number of times that address is found in the cache.

**2.6 Miss** box. The miss box records the number of times the address cannot be found in the cache.

**2.7 Hit Ratio** box. The ratio box records the fraction found by dividing the number of hits by the total number of addresses.

**2.8 Address** box. The address box displays the three components of the address, tag, index, and byte for each new address generated.

**2.9 Data** box. The data box displays the contents of the address given in the Address box. Eight hexadecimal digits are displayed.

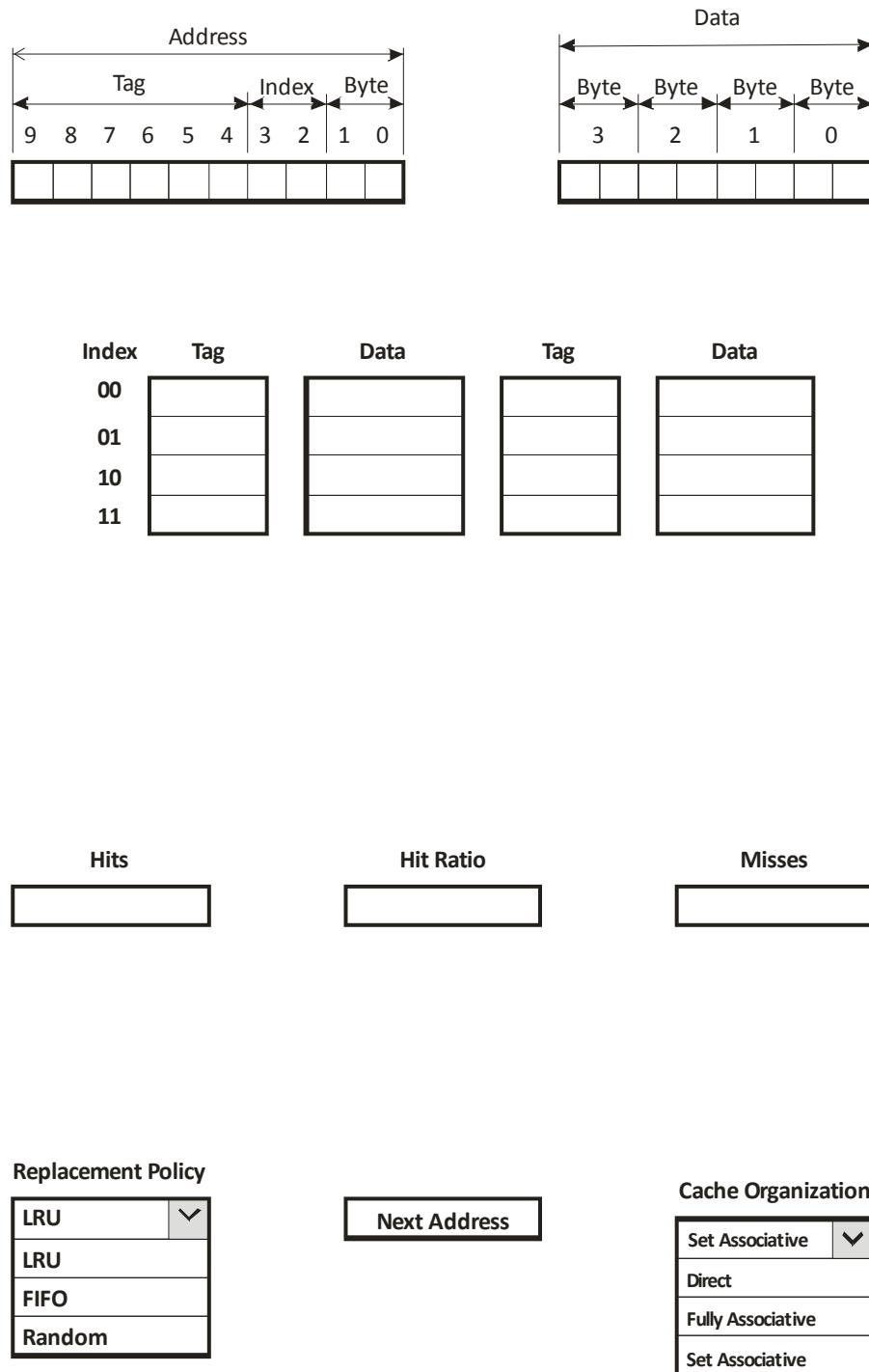

### 3 Set Associative Cache

**Figure 3.** Set Associative Cache Display

**3.1 Cache Organization** drop-down list. The Cache Organization drop-down list is used to select a **Set Associative** Cache Simulation.

**3.2 Replacement Policy** drop-down list. The Replacement Policy drop-down list permits one of three selections: **LRU**, **FIFO**, or **Random**. When LRU is selected the cache replaces the least recently used tag and data in the event of a cache miss. When FIFO is selected the cache replaces the oldest tag

and data in the cache in the event of a cache miss. When Random is selected the cache random selects a tag and data to replace on a cache miss.

**3.3 Next Address** button. The Next Address button is used to solicit a new address and data. The new address and data are displayed in the Address and Data boxes. The address is divided into three parts, tag, index, and byte as shown. The address is displayed in binary. Data are represented in hexadecimal.

**3.4 Cache** display. The cache is displayed as five columns where each column has half as many rows as there are index values in the direct-mapped cache. Since the index in the direct-mapped cache has three (3) bits, there are eight (8) rows in the direct-mapped cache and **four (4)** rows in the set associative cache. The columns are labeled **Index**, **Tag**, **Data**, **Tag**, and **Data** respectively. Tags are displayed in binary. Data are displayed in hexadecimal. Index values are fixed as labels for each row.

Each row is a set. The replacement policy is applied to each set. Highlighting is employed to identify the following

- The tag and data in the cache corresponding to the current address and data shown in the address and data boxes are given a middle highlight value.

- The cache tag and data that are replaced are given the brightest highlight.

- In every set the next tag and address to be replaced is highlighted using the lowest level highlight.

**3.5 Hit** box. The hit box records the number of times that address is found in the cache.

**3.6 Miss** box. The miss box records the number of times the address cannot be found in the cache.

**3.7 Hit Ratio** box. The ratio box records the fraction found by dividing the number of hits by the total number of addresses.

**3.8 Address** box. The address box displays the three components of the address, tag, index, and byte for each new address generated.

**3.9 Data** box. The data box displays the contents of the address given in the Address box. Eight hexadecimal digits are displayed.